When it comes to reset, we are all familiar with it. The system basically has a reset button. There are many types of reset: power-on reset, power-down reset, reset pin reset, watchdog reset, software reset, etc. This article discusses how to design the reset circuit in stm32.

STM32 introductionThe STM32 series is based on the ARM Cortex®-M0, M0+, M3, M4 and M7 cores specially designed for embedded applications requiring high performance, low cost, and low power consumption. France Semiconductor has launched STM32 basic series, enhanced series, USB basic series, and complementary series; the new series of products continue to use the 72MHz processing frequency of the enhanced series. The memory includes 64KB to 256KB flash memory and 20KB to 64KB embedded SRAM. The new series adopts three packages of LQFP64, LQFP100 and LFBGA100. Different packages maintain the consistency of pin arrangement. Combined with the design concept of STM32 platform, developers can re-optimize functions, memory, performance and pin count by selecting products to minimize Hardware changes to meet individual application requirements.

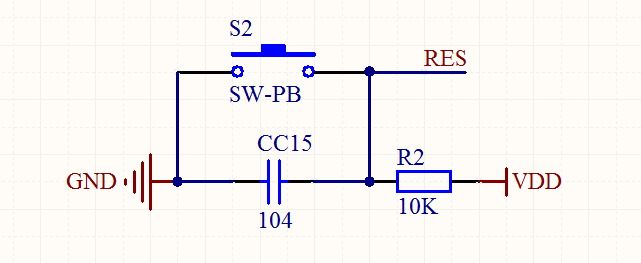

stm32 reset circuit designThe function of the reset circuit is to restore the system to its initial state. There are also several ways to reset the microcontroller: power-on reset, system reset, and backup area reset

Power-on reset: The condition is that a power-on reset occurs when the system is powered on, powered down, and when the system returns from standby mode. The power reset can reset the state of all registers except the backup area register.

System reset: A system reset can be generated when any of the following events occurs:

1. Low level on the NRST pin (external reset)

2. Window watchdog counting is terminated (WWDG reset)

3. Independent watchdog count termination (IWDG reset)

4. Software reset (SW reset)

5. Low power management reset

The system reset can reset all registers except the reset flag in the clock control register CRS and the registers in the backup area.

Backup area reset: For the reset of the backup area, one is generated by setting the corresponding bit in the backup area control register when the software is reset; the other is generated when the power supply and the battery are powered off and on again.

There are two commonly used reset methods. One is the low-level reset of the NRST pin. The button reset circuit gives this pin a low-level to allow the system to complete the reset. The other is known to everyone, that is, up. Electric reset, sometimes the reset circuit fails inexplicably, and sometimes when it is just started, although there are not as many reset circuits as buttons, it can be regarded as a very common reset method. The button reset circuit is directly shown in the diagram, and the online explanation may make the circuit diagram bad, so I don’t have to talk about it.

Calculation of capacitor charging time: T = 1.1RC = 1.1 * 10000 * 0.0000001 = 0.0011s = 1.1ms

The difference between kernel reset and system reset

The kernel mentioned in this article refers to the processor core, which is MPU (Microprocessor Unit). For example, STM32F103, its core is the Cortex-M3 core.

The system here includes the core and peripherals, which is the MCU (Microcontroller Unit). For the STM32F103, it is the Cortex-M3 core + various peripheral interfaces.

Core reset: Only reset the Cortex-M3 processor, but not the registers of peripherals such as GPIO, TIM, USART, SPI, etc.

System reset: Reset the Cortex-M3 processor and reset the peripheral registers.

Therefore, the reset we often refer to generally refers to system reset.

Kernel reset and system reset function source code

This article takes Cortex-M3 (STM32F103) as an example to illustrate, other chips are similar.

Write 4 reset functions, kernel reset (C language), kernel reset (assembly), system reset (C language), system reset (assembly):

void NVIC_CoreReset(void); //Core reset (C language)

void NVIC_CoreReset_a(void); //Core reset (assembly)

void NVIC_SystemReset(void); //System reset (C language)

void NVIC_SystemReset_a(void); //System reset (assembly)

The C language source code of NVIC_SystemReset has been provided in the core_cm3.h file in the ST official library.

Cortex-M3 allows the reset sequence to be triggered by software for special debugging or maintenance. In Cortex-M3, there are two ways to realize self-reset.

The first method: Set the VECTRESET bit (bit offset: 0) of the application interrupt and reset control register (AIRCR) in the NVIC.

NVIC_CoreReset core reset

The scope of this reset covers the entire Cortex-M3 processor, except for all corners of the debugging logic, but it will not affect any circuits outside the Cortex-M3 processor, so the on-chip peripherals and other on the STM32 The circuit is not affected.

C language source code of NVIC_CoreReset function written:

staTIc __INLINE void NVIC_CoreReset(void)

{

__DSB();

//Set VECTRESET

SCB-" AIRCR = ((0x5FA "" SCB_AIRCR_VECTKEY_Pos) |

(SCB-"AIRCR & SCB_AIRCR_PRIGROUP_Msk) |

SCB_AIRCR_VECTRESET_Msk);

__DSB();

while(1);

}Assembly version function source code:

__asm ​​void NVIC_CoreReset_a(void)

{

LDR R0, =0xE000ED0C

LDR R1, =0x05FA0001 //Set VECTRESET

STR R1, [R0]

deadloop_Core

B deadloop_Core

}

Kernel reset main attention: SCB_AIRCR_VECTRESET_Msk and LDR R1, =0x05FA0001, this is the only difference from system reset.

The second method: Set the SYSRESETREQ bit (bit offset: 2) in the application interrupt and reset control register (AIRCR) in the NVIC.

NVIC_SysReset system reset

The system reset is to set the SYSRESETREQ bit in the same register. This reset will affect the entire circuit on the chip: it will cause the Cortex-M3 processor to assert the request line sent to the system reset generator. However, the system reset generator is not a part of Cortex-M3, but is implemented by the chip manufacturer, so different chips respond differently to this reset. Therefore, readers need to read the chip specification carefully to understand what initial state each peripheral and functional module will return to when an on-chip reset occurs, or which functional modules will not be affected (for example, STM32 series chips have backup Storage area, the area is treated specially).

In most cases, when the reset generator responds to SYSRESETREQ, it will also assert the system reset signal (SYSRESETn) of the Cortex-M3 processor at the same time. Generally, SYSRESETREQ should not reset the debug logic.

There is a problem to pay attention to: there is often a delay from when SYSRESETREQ is set to valid to when the reset generator executes the reset command. During this delay, the processor can still respond to interrupt requests. But our original intention is often to let this execution end here and not to do anything else. Therefore, it is best to set FAULTMASK before issuing a reset request. The following assembly statements can be used: __disable_fault_irq();.

The C language source code of the NVIC_SystemReset function provided in core_cm3.h:

staTIc __INLINE void NVIC_SystemReset(void)

{

SCB->AIRCR = ((0x5FA

(SCB->AIRCR & SCB_AIRCR_PRIGROUP_Msk) |

SCB_AIRCR_SYSRESETREQ_Msk);

__DSB(); /* Ensure compleTIon of memory access /

while(1); /* wait unTIl reset */

}

Assembly function:

__asm ​​void NVIC_SysReset_a(void)

{

LDR R0, =0xE000ED0C

LDR R1, =0x05FA0004

STR R1, [R0]

deadloop_Sys

B deadloop_Sys

}

ConclusionSome systems allow resetting, but have special requirements for peripherals: a certain IO state cannot be changed due to reset, a certain timer counter cannot be changed, etc. Example: System A controls the power supply of System B through an IO, and the power of System B is turned on when this IO is set to high.

In the normal working process, the B system will shut down only when it receives the A system shutdown command task (that is, it cannot be shut down by power down), and the A system needs to be reset during the working process.

At this time, if the conventional reset method is used, the IO will be reset, which does not meet the requirements. It would be great if there was a way to reset the core without resetting the peripherals.

This is the end of the related introduction about the stm32 reset circuit. I hope this article will give you a deeper understanding of the stm32 reset circuit. If there are any shortcomings, you can look forward to it.

Perfect fit: The Hydrogel Screen Protector is designed with a Soft TPU material, which can be completely covered even on a curved device, providing perfect protection for the full coverage of the screen.

Oleophobic and waterproof: The use of hydrophobic and oleophobic screen coatings can prevent sweat, grease residue and fingerprints without reducing screen sensitivity. It is almost invisible on the screen and brings a high-definition visual experience.

Sensitive touch: ultra-thin and Soft Hydrogel Film with a thickness of only 0.14mm. As time goes by, it will self-repair minor scratches, provide you with a highly responsive screen protector and maintain the original touch.

Easy to install: The installation of the Protective Film is very simple, without air bubbles. The protective sticker can stay on the phone perfectly, and the bubbles will disappear within 24 hours.

If you want to know more about Hydrogel Screen Protector products, please click the product details to view the parameters, models, pictures, prices and other information about Hydrogel Screen Protective Film.

Whether you are a group or an individual, we will try our best to provide you with accurate and comprehensive information about the Hydrogel Protective Film!

Hydrogel TPU Protective Film,Ultra-Thin Protective Film,Soft Hydrogel Film,Hydrogel Film Screen Protector,Screen Protective Film,Mobile Phone Screen Guards

Shenzhen Jianjiantong Technology Co., Ltd. , https://www.jjtscreenprotector.com