When I first started playing the CPLD/FPGA development board, I used an EPM240T100-based board. Although this chip of alter has small power consumption and small size, the resources are still very small. You can write a slightly more complicated program. If you don’t pay attention to the coding style , It is easy to overflow. At that time, doing a three-digit decoding basically made me suffer, and I have a deep understanding of the importance of coding style.

Later, because I have been playing xilinx's spartan3 xc3s400, this chip has very rich resources, and I even cached a frame of 640*480*3/8BYTE data in it without any problem (for VGA display). However, I recently contacted EPM7128, its resources do not seem to be rich, I wrote that sometimes it is impossible to wire without paying attention. This shows the importance of coding style to the design, especially in the design with tight resources or high speed requirements. I personally have a deeper understanding of the former. I have not involved in high-speed design. I just understand some methods to increase speed with assembly lines.

You can get to the point, let's start with a simple piece of code. Let me mention one point first. This time I used quartus II 7.0 for testing. The RTL views synthesized by other EDA tools may be different, so just use it as a reference in the quartus II 7.0 environment. But the idea is the same, and we can learn from it.

Ex1:

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0);

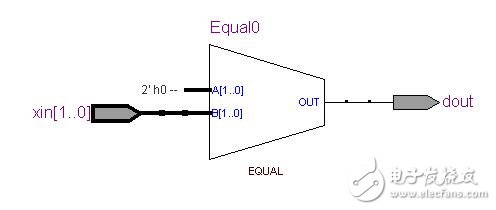

The code is very simple, that is, dout=1 when xin==2'b0, otherwise dout=0. The RTL view of the above program is as follows:

In fact, it is a comparator, if xin=2'h0, then the output OUT is 1. The same as imagined.

The following is a common way that I see others when I refer to some other people's code. It uses the? Statement.

input[1:0] xin;

output dout;

assign dout = (xin == 2'b0)? 1'b1:1'b0;

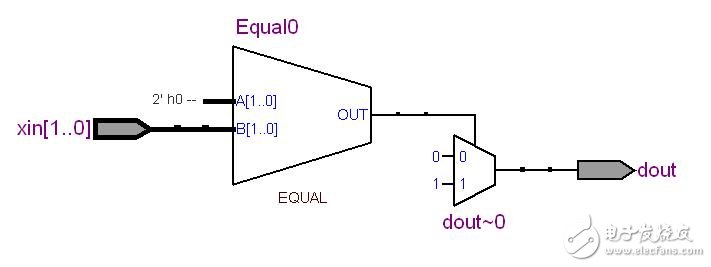

The RTL is as follows:

Did you find that there is an extra selector (maybe not called a selector, but you can understand the meaning), so that it consumes a little more resources for no reason. At the beginning, I was stupid to follow others to use this Written, but after seeing the RTL view, I don’t do that. Since the former can also get the expected results, why should I add an extra selector? Therefore, the former is recommended. The saving of resources is imperceptible~_~

(Let’s talk about it first, let me mention the rest when I think of it or feel it, the above is also my personal humble opinion, if there is anything wrong, please make a brick~_~)

Wall Mount Digital Signage,Touch Screen Digital Displays,Advertising Led Display Screen,Wall Mount Digital Signage Player

APIO ELECTRONIC CO.,LTD , https://www.apiodisplays.com