After understanding the Zynq PS / PL interface; so far, we have analyzed the interface between PS (processor system) and PL (programmable logic) in the Zynq All Programmable SoC chip. We have created a simple peripheral using the Vivado Design Suite, connected to the new peripheral using the SDK, and can run a self-test on the peripheral. But we created peripheral functions that do not exceed four registers that can be read and written. In fact, we need peripherals to perform some useful functions.

We will use Vivado again to add the actual functionality to this peripheral.

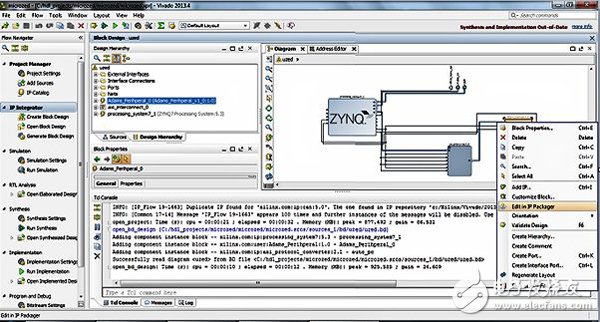

First you need to open the Vivado project and the block diagram, which contains the peripherals we have created. Right click on "Peripheral" and select the "Edit IP Packager" option. The IP Packager window will then open to edit and update the peripherals.

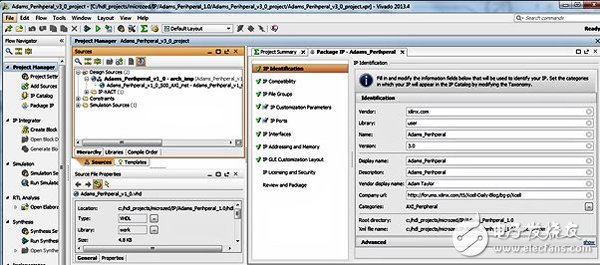

This window is similar to the standard project stream window except for the Package IP Peripheral window. Below the Design Source window are two files created during the peripheral creation process.

These files are named as:

Adams_Peripheral_v1_0.vhd - A top-level schema file that allows you to define user I/O exiting the module.

Adams_Peripheral_V1_0_S00_AXI.vhd - RTL file containing the function AXI interface, including the four registers initially created.

These two files include an annotation that the user code will insert the address:

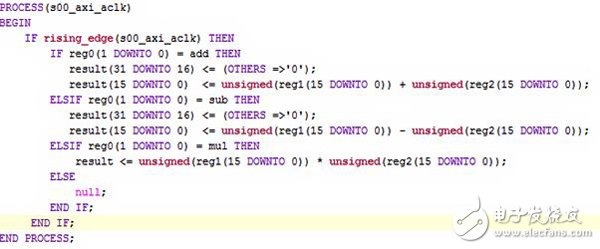

In this example, I will introduce the use of the first register as a control register. The specific bits in this register define whether the registers of registers 2 and 3 are added, subtracted, or multiplied. The result of the operation will be stored in the fourth register. We will set the fourth register associated with the microprocessor to read-only to ensure that the microprocessor does not affect the result of the operation. In addition, if the control register is activated, the peripheral will generate an interrupt.

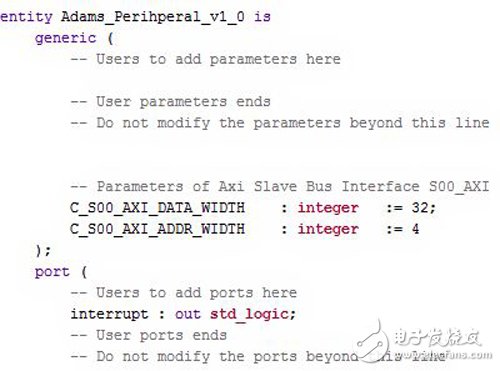

The first step in the definition is to declare four registers, the third register is the output register, and the last one is the input register. (We can do this at this step, but I am currently working on the top level to demonstrate the steps required to implement more complex functions).

At the same time, I also edit this file as a read-only file to prevent the processor from writing to the fourth register.

In the top-level file I create an interrupt output in the schema and add simple function code to perform the operation we want.

After all the necessary user VHDL languages ​​have been added, I processed the project to ensure that there is no error before packaging the IP in Vivado and returning to the project. But before the packager packs the IP, I add the IP version number to indicate the code change. Clicking on "re-package" will run the packager and close the project to return to the original Vivado project.

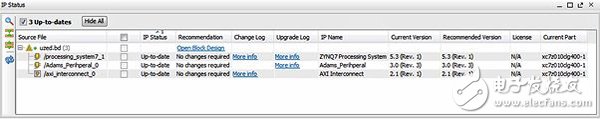

Returning to the project using this peripheral, you can run the IP Status Report (Tools ->Reports ->Report IP status) to display the updated version used in the design.

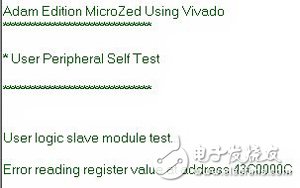

You need to rebuild the project before exporting the project to the SDK. Within the SDK, this peripheral can be written and read using the same function previously used. However, the self-test will fail when the last register in the test cannot be written.

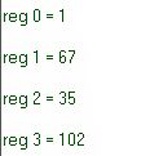

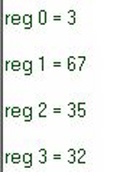

The first test is to add the contents of registers 2 and 3 using command 1 in register 0:

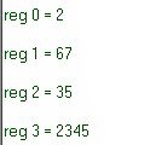

In the second test, we multiply the directories in registers 2 and 3 using command 2 in register 0:

In the final test, we used the command 3 in register 0 to subtract the directory in register 2 from the directory of register 3:

All of these tests use the polling method. Since these operations are simple addition, subtraction, and multiplication functions, they can be completed in one clock cycle. But more complex multi-cycle function operations require the use of interrupts, which we will cover in another article.

Cooler pump Magnet 16x25,water pump magnet,ferrite magnet moulded

HU NAN YUBANG MAGNETIC MATERIAL CO.,LTD , https://www.ybmagnet.com