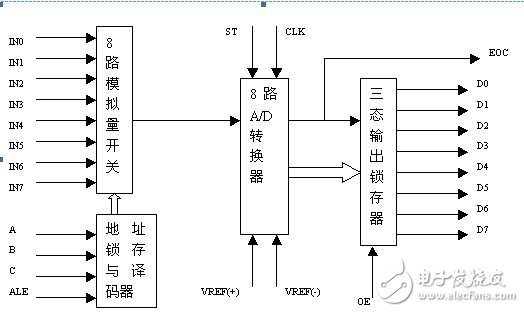

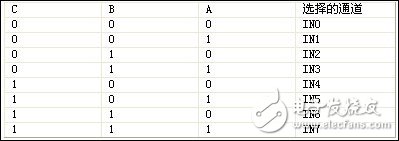

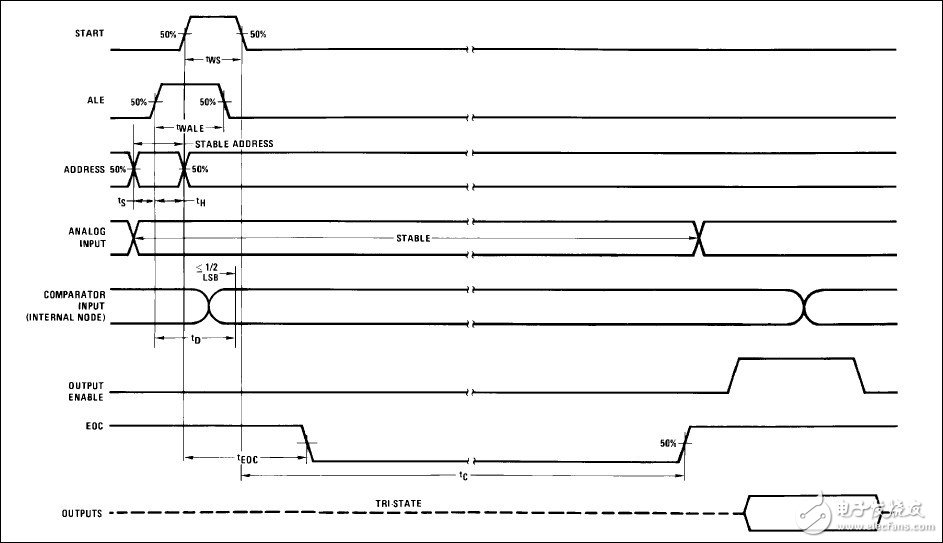

In the previous article, I wrote a general signal generator based on Xilinx FPGA. The response is better. Many friends and I discussed related technologies, including the signal acquisition. In order to make the article more flesh and blood, I am writing a The general signal collector of Xilinx FPGA hopes to form an echo to answer your questions. Purpose: 1. Through the design to achieve signal acquisition and analysis, master the combination logic design method; 2. Through the design to achieve signal acquisition and analysis, master the principle of signal acquisition. Principle: Using FPGA chip, write logic in verilog language, control AD0809 for AD conversion. The AD0809 is a CMOS component with an 8-bit AD converter, 8-way multiplexer, and microprocessor-compatible control logic. It is a successive approximation AD converter. The internal structure of AD0809 is as follows:

Electric iron is a tool for leveling clothes and fabrics, and its power is generally between 300-1000W. Its types can be divided into: ordinary type, temperature adjustment type, steam spray type and so on. Ordinary electric irons are simple in structure, low in price, and convenient to manufacture and maintain. The temperature-regulating electric iron can automatically adjust the temperature within the range of 60-250℃, and can automatically cut off the power. It can be ironed at a suitable temperature according to different clothing materials, which is more power-saving than the ordinary type. Steam spray type electric irons not only have the function of temperature adjustment, but also generate steam. Some are also equipped with a spray device to avoid the trouble of manual water spraying, and the clothes are more evenly moistened and the ironing effect is better.

ShenZhen YouTai Imp.& Exp. Co., Ltd. founded in 2014, headquartered in Shenzhen, which is a leading supplier of high-tech ODM/OEM One-Stop services for smart Home Appliances, Kitchen Appliances, Consumer Electronics.Our strategic partnership have TCL, Skyworth, Lenovo and Medea. Our customers are from more than 10 countries. We committed to manufacture and provide customers high performance and high value of innovative electronic products.Welcome to inquiry about us!

Mini Electric Irons,Household Electric Irons,Portable Electric Irons

Shenzhen YouTai Imp.&Exp.,Co.,Ltd. , https://www.szyoutai-tech.com