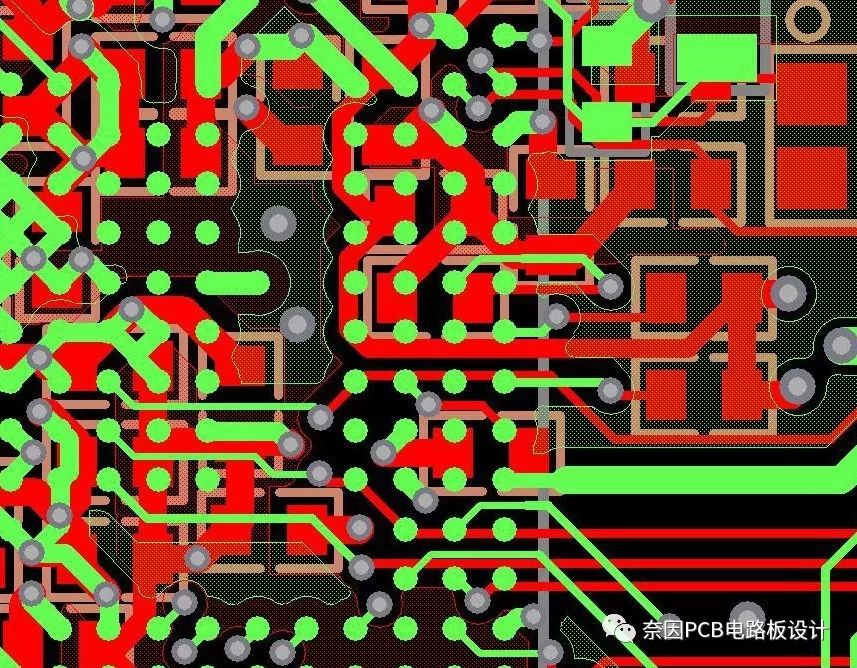

For the design of vias in high-speed PCBs, most of them are through the analysis of the parasitic characteristics of vias. We can see that usually in the process of high-speed PCB design, the seemingly simple vias usually give the design of the circuit. Come a big negative effect.

Therefore, in order to reduce the adverse effects of the parasitic effects of vias, we can try to do the following in the design:

1. Select a reasonable size of the hole from the viewpoint of cost and signal quality. For example, for a 6-10 layer memory module PCB design, a 10/20Mil (drill/pad) via is preferred, for some small high-density boards.

You can also try using 8/18Mil vias. Under current technical conditions, it is more difficult to use the hole to be smaller in size. For vias for power or ground, larger sizes can be considered in order to reduce impedance.

2, the above two formulas can be concluded that the use of a thin PCB board is beneficial to reduce the two parasitic parameters of the via.

3. The signal line does not change on the PCB layer, that is, try not to use unnecessary vias.

4. The pin of the power supply and ground should be drilled nearby. The shorter the lead between the via and the pin, the better, because they will increase in the inductance. At the same time, the power and ground leads should be as thick as possible in order to reduce the impedance.

5. Place some grounded vias near the vias of the signal-changing layer in order to provide the latest signal to the circuit. It is even possible to place a large number of redundant ground vias on the PCB. Of course, you need a flexible design.

The perforated model discussed above is that everyone has pads, and sometimes, we can reduce some keyboards or even cancel layers. Especially in the case of very high via density, it may cause a broken channel in the copper layer to form a partition circuit.

To solve such a problem, in addition to moving the position of the via hole, the through hole of the pad can also be considered to reduce the size of the copper layer.

Cable Gland,Power Cable,Cable Clips,Cable Organizer

Changshu Herun Import & Export Co.,Ltd , https://www.herunchina.com